# design your future

# DESIGN AND DEVELOPMENT OF AN AUTOMATED TEST BENCH FOR SONAR ELECTRONICS

VIVES Technology

Bachelor in electronics-ICT

Campus Kortrijk

Luján María

Vynckier Ilias

Academic year 2021-2022

# DESIGN AND DEVELOPMENT OF AN AUTOMATED TEST BENCH FOR SONAR ELECTRONICS

VIVES Technology

Bachelor in electronics-ICT

Campus Kortrijk

Luján María

Vynckier Ilias

Academic year 2021-2022

### **Preface**

This thesis named 'Design and Development of an Automated Test Bench for Sonar Electronics' has been written as the last milestone of our four months internship being part of the ECA Robotics engineering team.

As ECA Robotics Belgium is still a newly created branch of ECA Group, we have been able to watch a lot of the steps that had been and will be taken to make ECA Robotics a leading company among underwater military drone suppliers in Belgium. We were part of the engineering team, developing the first design of this test bench for Sonar Electronics. The remarkable part was that we were working there as if we were full-fledged employees. We can proudly reveal that the final design based on our work will be included in the production line in the near future.

The project was appealing for us from the beginning. The opportunity to work in a field related to the manufacturing and design of something as notable as underwater robots was one of the things that made us choose the company.

The thesis proposal was also attractive to us. We had quite some experience in microcontroller programming and software design on Linux, which are the main components of this project. The advantages of working for a yet not-so-big company, more employee-oriented, was something we had in mind too when deciding the environment where our bachelor thesis was going to be developed.

We want to remind the reader that, due to working for a private company and furthermore for one that works in cooperation with military institutions, some parts or details of the software and technology used in this project cannot be discussed with the general public. All information contained in this document has been reviewed and approved by the company in order to be published without constraints.

We both are very grateful to ECA Robotics for letting us be here these past months. The team was very welcoming, and we want to especially thank them for guiding us so well and sharing all the knowledge they could with us. Also, we want to strongly thank them for make us feel as an active part of the company and the team.

We would like to take this opportunity to express our gratitude to some people in our personal name.

I, Ilias, would like to thank my internship supervisors at ECA Robotics Belgium. Thank you Bastien Loisy, Bjorn Declercq, Guillaume Villee, Dominique Aernout and Jeroen Debonnet for the guidance during the fascinating internship period. Furthermore, I would like to thank my Vives mentor Tom Termote for his helpful feedback and guidance during the writing of our bachelor thesis. Thirdly, I would like to thank my fellow student, Maria. Thanks for the good teamwork, the pleasant internship period and the critical view of our internship project. Without you, our bachelor thesis would not have become what it is now! Furthermore, I would like to thank my sister, Esther, for the tips she gave me during the process of writing my bachelor thesis. I also wish to acknowledge all

the people who have helped me over the years. Finally, I would like to thank my parents for giving me the opportunity to follow this fascinating study programme.

I, María, in first place want to thank Ilias for being an amazing bachelor thesis partner, and to Tom Termote for all the help and for the faith he put on us and our work. Also, as said before, to all the ECA team that guided us so well through the development of this project.

As this is one of the final steps to get my diploma, I want also to acknowledge the people that have been with me all these years back in Spain:

I want to first thank my parents. I am who and where I am because of them and the infinite patience, care, and attention they have put in the education of their children. Not only academically, but in every other aspect of our lives.

Also, the rest of my family, for always supporting me and being the best example one can have. Specially my grandparents because a grandchild couldn't ask for better role models.

Thanks too to my high school friends that believed in me since day one, and never doubted I would finish this thing.

And finally, thanks to my lil-chuchoshot for being the ray of sunshine of my bachelor's degree and my life in general for the past five years.

Ilias & María

### **Abstract**

This thesis aims to be a first approach for the development of a test bench capable of performing automatic tests on an electronic board and reporting back the results to the user.

The general project set sights on implementing this test bench in the production line of a sonar developed by ECA Robotics, that will be mounted into the underwater drone toolbox that they, in collaboration with Naval Group, will provide to the Belgian and Dutch navies for Mine Warfare Countermeasure purposes.

Specifically, the main targets of this thesis are to evaluate the feasibility of the idea and to test the concept of it. For that, a PC application and the software for a microcontroller was designed and developed, as well as the communication between them using a customized protocol.

After implementing this design - using a prototype - a functional automated testbench was built, which verified the concept that had to be attested.

# **Table of contents**

| Pref | ace 3                           |

|------|---------------------------------|

| Abs  | tract 5                         |

| Tab  | le of contents 6                |

| List | of figures9                     |

| List | of tables11                     |

| Sym  | bols and abbreviations used12   |

| 1    | Introduction14                  |

| Mot  | ivation14                       |

| Obje | ectives14                       |

| Dev  | elopment timeline15             |

| Stru | cture of the document15         |

| 2    | Background17                    |

| Auto | onomous Underwater Vehicle17    |

| Terr | ninology17                      |

| Defi | nitions and history17           |

| Son  | ar18                            |

| Defi | nitions and terminology18       |

| Hist | ory19                           |

| Phy: | sical principles19              |

| Clas | sification20                    |

| RX3  | 222                             |

| Test | Bench23                         |

| Terr | ninology23                      |

| Nuc  | leo-14423                       |

| Abo  | ut the manufacturer23           |

| Feat | tures23                         |

| 3    | Context of the project25        |

| Wha  | at is a naval mine?25           |

| The  | history of naval mine warfare25 |

| Applicable regulations on naval mine warfare             | 27 |

|----------------------------------------------------------|----|

| Reality of current underwater mine warfare threats       | 27 |

| Nowadays Mine Countermeasures (MCM)                      | 28 |

| Future of MCM: Belgium Naval & Robotics                  | 28 |

| The mine-hunter drone system for BE/NL Navy              | 29 |

| UMIS™ sonar: UMISAS                                      | 31 |

| The electronics of SAS and the approach of their testing | 32 |

| 4 Technical explanation                                  | 33 |

| General view                                             | 33 |

| Project vision and scope                                 | 34 |

| Use cases                                                | 34 |

| Communication                                            | 37 |

| Protocol                                                 | 38 |

| PC part                                                  | 39 |

| Coding language                                          | 39 |

| Code                                                     | 39 |

| Serial connection                                        | 41 |

| Test sequencer                                           | 42 |

| GTK main loop and single Threading                       | 44 |

| Test                                                     | 45 |

| Database                                                 | 45 |

| PDF                                                      | 47 |

| Nucleo part                                              | 48 |

| STM32CubeIDE                                             | 48 |

| MCU configuration                                        | 48 |

| Software description                                     | 52 |

| Peripheral drivers                                       | 52 |

| Management unit                                          | 59 |

| STM32CubeIDE files                                       | 61 |

| Hardware                                                 | 61 |

| Filter for the Nucleo DAC                                | 62 |

| Tens | sion divisor for DC/DC converter peripheral | 63 |

|------|---------------------------------------------|----|

| Test | t bench prototype                           | 64 |

| 5    | General conclusion                          | 66 |

| Tech | hnical conclusion                           | 66 |

| Pers | sonal conclusion                            | 66 |

| 6    | Bibliography                                | 67 |

| 7    | Annexes                                     | 70 |

| Time | eline                                       | 70 |

| UMI  | L diagrams                                  | 71 |

| GPIC | O read function                             | 72 |

| Sine | e wave form function                        | 73 |

| Wat  | tchdog driver substitute function           | 73 |

| Inco | oming message divider function              | 74 |

| DAC  | C signal after low pass filter              | 74 |

| MCl  | U-PC Communication Comparison               | 76 |

# List of figures

| FIGURE 1: ADAPTED FROM BLONDEL, P. (2009A). DEFINITIONS OF SOME PARAMETERS [ILUSTRATION]. IN THE HANDBOOK O       |      |

|-------------------------------------------------------------------------------------------------------------------|------|

| SIDESCAN SONAR (P. 15).                                                                                           |      |

| $FIGURE\ 2\ [ACTIVE\ SONAR\ VS\ PASSIVE\ SONAR].\ (N.D.).\ HTTPS://WWW.RFWIRELESS-WORLD.COM/IMAGES/ACTIVE-SONAR.$ | R-   |

| vs-Passive-SONAR.jpg                                                                                              | 21   |

| FIGURE 3: NATIONAL OCEANIC AND ATMOSPHERIC ADMINISTRATION [NOAA]. (N.D.). SIDE-SCAN SONAR VS SYNTHETIC            |      |

| APERTURE SONAR PULSES [ILLUSTRATION]. NATIONAL OCEANIC AND ATMOSPHERIC ADMINISTRATION (NOAA) OCEAN                |      |

| EXPLORATION. HTTPS://OCEANEXPLORER.NOAA.GOV/TECHNOLOGY/SONAR/SAS.HTML                                             | 22   |

| FIGURE 4: ONI-37 & NAVAL HISTORY AND HERITAGE COMMAND. (N.D.). FLOATING MINE IN THE NORTH SEA 123952              |      |

| [PHOTOGRAPH]. NAVAL HISTORY AND HERITAGE COMMAND. HTTPS://WWW.HISTORY.NAVY.MIL/                                   | 25   |

| FIGURE 5: NAVAL HISTORY AND HERITAGE COMMAND & SIGNAL CORPS 43589. (N.D.). HANDLING MINE CASES. NH 12395          | 55   |

| [PHOTOGRAPH]. NAVAL HISTORY AND HERITAGE COMMAND. HTTPS://WWW.HISTORY.NAVY.MIL/                                   | 26   |

| FIGURE 6: ECA GROUP. (N.D.). INSPECTOR 125 [PHOTOGRAPH]. ECA GROUP.                                               |      |

| HTTPS://WWW.ECAGROUP.COM/EN/SOLUTIONS                                                                             | 29   |

| FIGURE 7: ECA GROUP. (N.D.). A18-M [PHOTOGRAPH]. ECA GROUP. HTTPS://WWW.ECAGROUP.COM/EN/SOLUTIONS                 | 29   |

| FIGURE 8: ECA GROUP. (N.D.). IMAGE OBTAINED WITH SAS [PHOTOGRAPH]. ECA GROUP.                                     |      |

| HTTPS://WWW.ECAGROUP.COM/EN/SOLUTIONS                                                                             | 30   |

| FIGURE 9: ECA GROUP. (N.D.). SEASCAN MK2 [PHOTOGRAPH]. ECA GROUP.                                                 |      |

| HTTPS://WWW.ECAGROUP.COM/EN/SOLUTIONS                                                                             | 30   |

| FIGURE 10: ECA GROUP. (N.D.). K-STER [PHOTOGRAPH]. ECA GROUP. HTTPS://WWW.ECAGROUP.COM/EN/SOLUTIONS               | 30   |

| FIGURE 11: ECA GROUP. (N.D.). UMISAS TOOLBOX [ILUSTRATION]. ECA GROUP.                                            |      |

| HTTPS://WWW.ECAGROUP.COM/EN/SOLUTIONS                                                                             | 31   |

| FIGURE 12: ECA GROUP. (2021, MARCH 31). UMISAS 120 VHF SONAR IMAGE OF S.S. FERRANDO COLLECTED OFF THE CO          | DAST |

| of Hyères, France. [Photograph]. Belgium Naval & Robotics. https://www.belgium-naval-and-                         |      |

| ROBOTICS.BE/SUCESSFUL-SEA-TRIALS-ECA-GROUP-UMISAS-SONAR/                                                          | 32   |

| FIGURE 13: SOFTWARE OVERVIEW DIAGRAM                                                                              | 33   |

| FIGURE 14: USE CASES DIAGRAM                                                                                      | 35   |

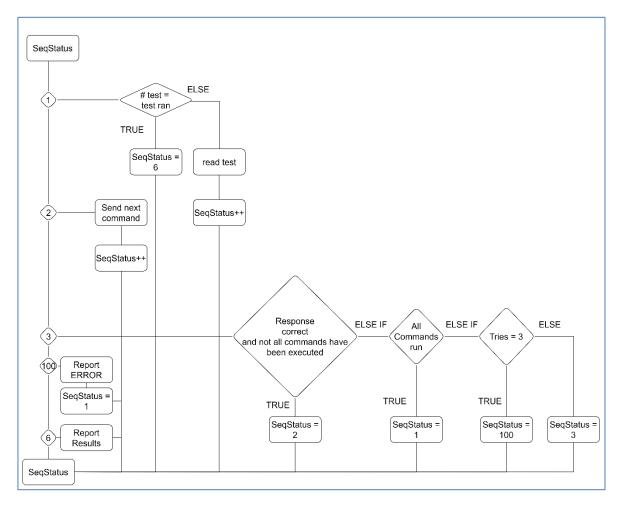

| FIGURE 15: FLOWCHART OF TEST SEQUENCER                                                                            | 42   |

| FIGURE 16: GLIB FUNCTIONS IN MAIN LOOP GUI                                                                        | 44   |

| FIGURE 17: POWER TEST                                                                                             | 45   |

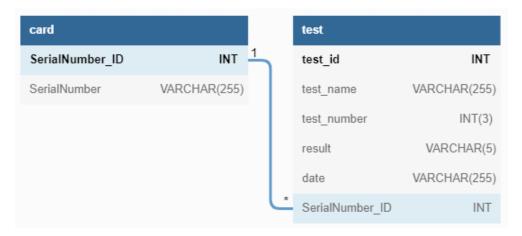

| FIGURE 18: TABLES OF THE DATABASE                                                                                 | 46   |

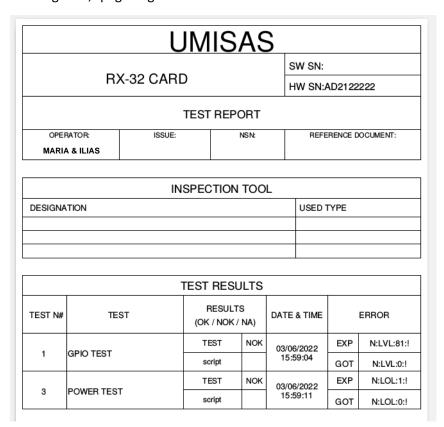

| FIGURE 19: EXAMPLE OF PFD-RAPPORT                                                                                 | 47   |

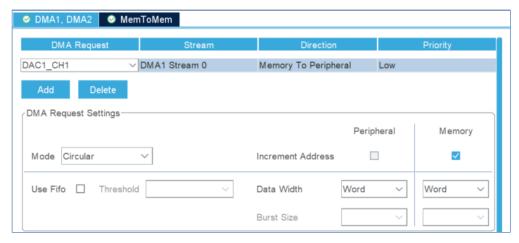

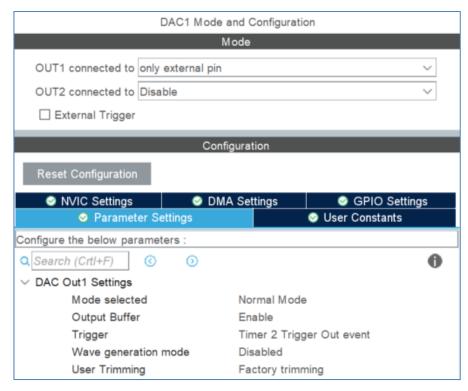

| FIGURE 20: DAC DMA CONFIGURATION                                                                                  | 49   |

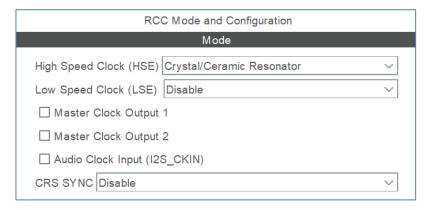

| FIGURE 21: RCC MODE AND CONFIGURATION.                                                                            | 49   |

| FIGURE 22: DAC1 MODE AND CONFIGURATION.                                                                           | 50   |

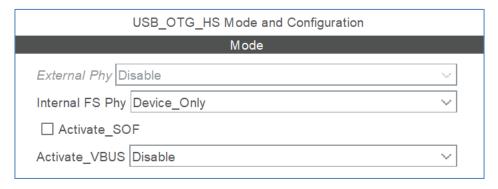

| FIGURE 23: USB_OTG_HS MODE AND CONFIGURATION.                                                                     | 51   |

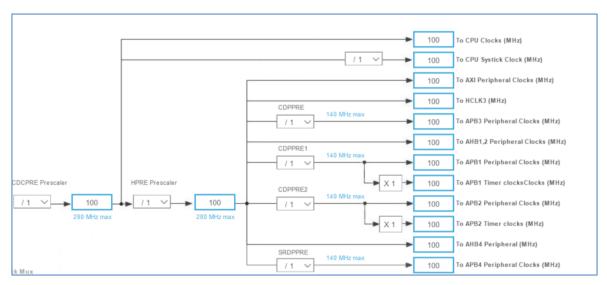

| FIGURE 24: CLOCK CONFIGURATION.                                                                                   | 52   |

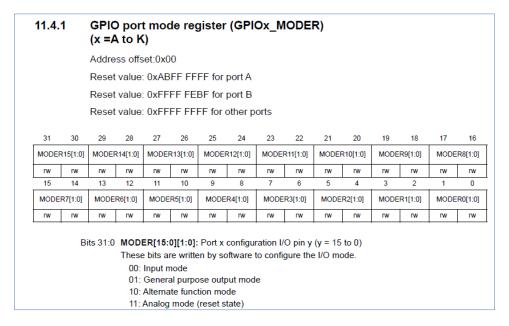

| FIGURE 25: STMICROELECTRONICS. (2022, JANUARY). GPIO PORT MODE REGISTER (GPIOX_MODER) [SCREENSHOT]. IN            |      |

| REFERENCE MANUAL. STM32H7A3/7B3 AND STM32H7B0 VALUE LINE ADVANCED ARM®-BASED 32-BIT MCUS                          |      |

| (RM0455 REV 8 ED., P. 517)                                                                                        | 53   |

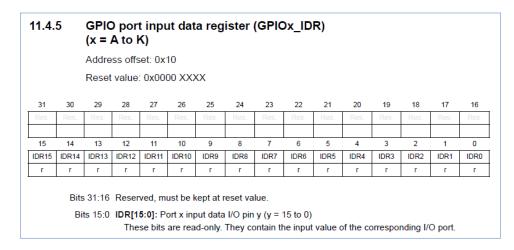

| FIGURE 26: STMICROELECTRONICS. (2022, JANUARY). GPIO PORT INPUT DATA REGISTER (GPIOX_IDR) [SCREENSHOT]. IN        |      |

| REFERENCE MANUAL. STM32H7A3/7B3 AND STM32H7B0 VALUE LINE ADVANCED ARM®-BASED 32-BIT MCUS                          |      |

| (RM0455 REV 8 ED., P. 517)                                                                                        | 53   |

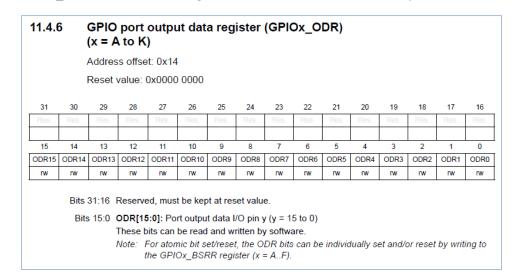

| FIGURE 27:STMICROELECTRONICS. (2022, JANUARY). GPIO PORT OUTPUT DATA REGISTER (GPIOX_ODR) [SCREENSHO      | )Τ]. IN |

|-----------------------------------------------------------------------------------------------------------|---------|

| REFERENCE MANUAL. STM32H7A3/7B3 AND STM32H7B0 VALUE LINE ADVANCED ARM®-BASED 32-BIT MCU                   | Is      |

| (RM0455 REV 8 ED., P. 517)                                                                                | 54      |

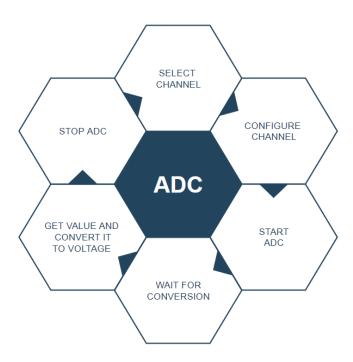

| Figure 28: ADC sequence diagram                                                                           | 56      |

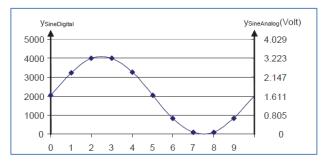

| FIGURE 29: STMICROELECTRONICS. (2020, JUNE). SINE WAVE MODEL SAMPLES [FIGURE]. IN APPLICATION NOTE: AUDIO | ) AND   |

| WAVEFORM GENERATION USING THE DAC IN STM32 PRODUCTS                                                       | 57      |

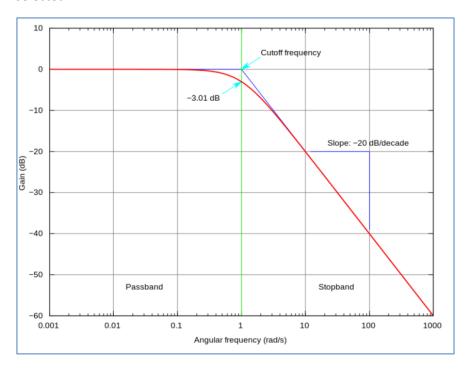

| Figure 30: Low pass filter Bode diagram                                                                   | 62      |

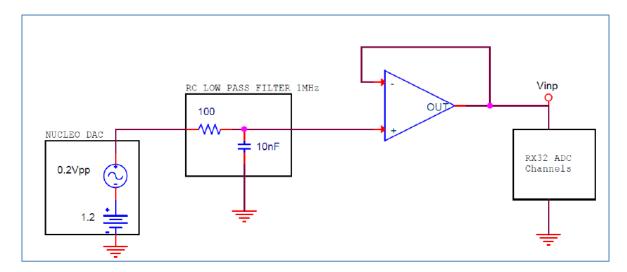

| FIGURE 31: CIRCUIT SCHEMATIC FOR THE DAC SINE WAVE GENERATION                                             | 63      |

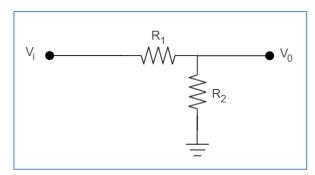

| Figure 32: Tension divisor electrical schematic                                                           | 63      |

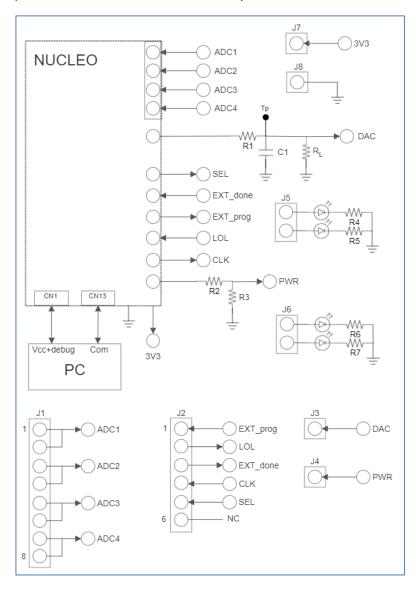

| FIGURE 33: TEST BENCH PROTOTYPE ELECTRIC DIAGRAM                                                          | 64      |

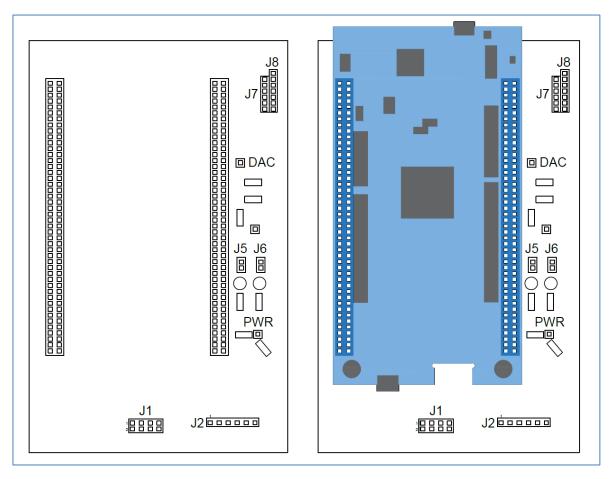

| FIGURE 34: TEST BENCH PROTOTYPE PCB SCHEMATIC WITH AND WITHOUT THE NUCLEO PLUGGED IN                      | 65      |

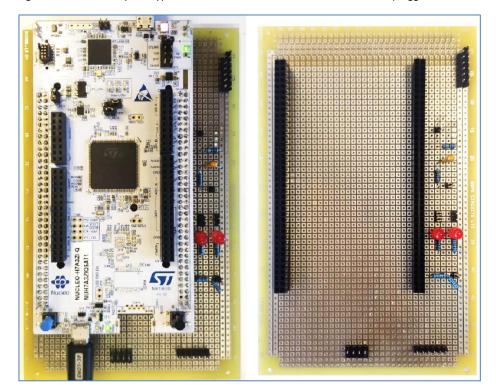

| FIGURE 35: [PHOTOGRAPH] TEST BENCH PROTOTYPE PCB WITH AND WITHOUT THE NUCLEO PLUGGED IN                   | 65      |

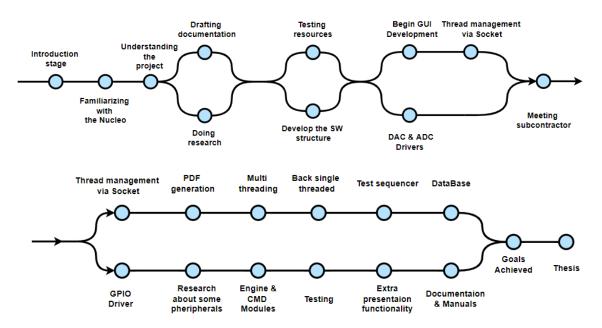

| FIGURE 36: PROJECT TIMELINE                                                                               | 70      |

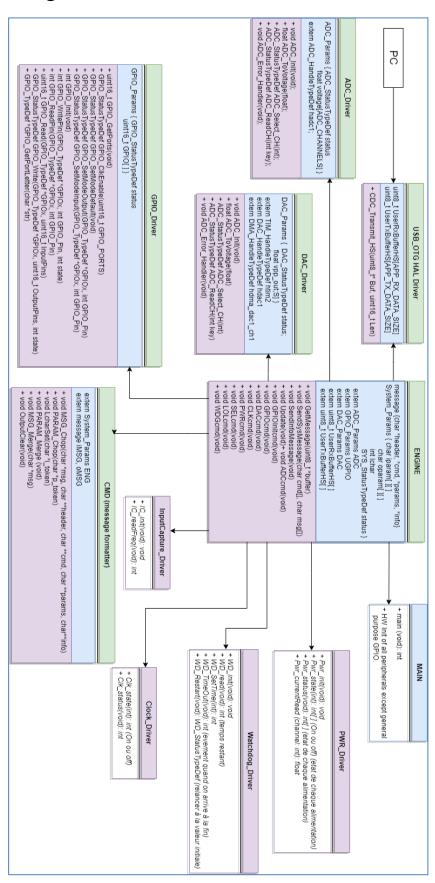

| Figure 37: Nucleo UML diagram                                                                             | 71      |

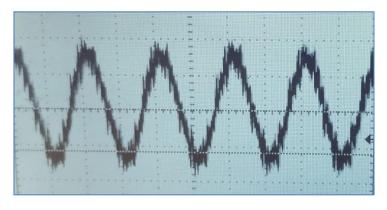

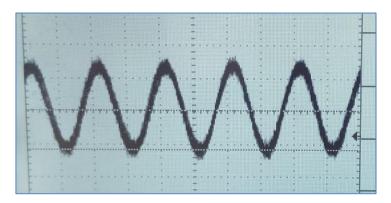

| Figure 38: Output signal with no filter                                                                   | 74      |

| FIGURE 39: OUTPUT SIGNAL WITH RC LOW PASS FILTER                                                          | 75      |

# **List of tables**

| Table 1: Actor and target identification           | 34 |

|----------------------------------------------------|----|

| TABLE 2: USE CASE. UUT'S SYSTEMS PERFORMANCE CHECK | 36 |

| TABLE 3: USE CAE. POWER GENERATION                 | 36 |

| TABLE 4: USE CASE. CLOCK SIGNAL GENERATION         | 37 |

# Symbols and abbreviations used

**AUV.** Autonomous Underwater Vehicle

**DMO.** Defence Material Organization

FPGA. Field Programable Gate Array

**GPS.** Global Positioning System

HS. High Speed

HSE. High-speed External Oscillator

IDR. Input Data Register

InSAS. Interferometric Synthetic Aperture Sonar

LED. Light-emitting diode

**MCM.** Mine Countermeasures

MCWP. Marine Corps Warfighting Publication

MIW. Mine Warfare

**MODER.** Port Mode Register

NATO. North Atlantic Treaty Organization

NOAA. National Oceanic and Atmospheric Administration

**NVIC.** Nested Vector Interrupt Controller

NWP. Naval Warfare Publication

**ODR.** Output Data Register

OTG. On The Go

PCB. Printed Circuit Board

PHY. Physical Interface

**RCC.** Reset and Clock Control

RMS. Royal Mail Ship

**ROV.** Remotely Operated Vehicle

SAS. Synthetic Aperture Sonar

**SONAR.** Sound navigation and ranging

SSS. Side-scan sonar

TIM. Timer

**UAV.** Unmanned Aerial Vehicle

**UMIS.** Unmanned MCM Integrated System

**UUT.** Unit Under Test

**UUV.** Unmanned Underwater Vehicle

### 1 Introduction

The prevalence of naval mines in almost all seas poses a major threat to both commercial and military vessels. Nowadays, demining operations are carried out by specialised military teams, most notably those of the Belgian and Dutch navies.

Today, this dangerous task is aided by drones, which avoid endangering human lives, and go deep into minefields to identify and dispose the explosive devices safely.

The partnership formed by ECA Robotics Belgium and Naval Group aims to provide a next generation drone system for mine countermeasure missions for the Belgian and Dutch navies. This bachelor thesis is part of the development of one of these drones, specifically focused on its sonar and the electronics that compose it.

### Motivation

As the project develops, more units of drones and sonars mounted on them are being produced after the prototypes' performance met the expectations. The number of units to be produced make efficient testing a crucial part of the production chain. Due to this, the company has decided to implement an automatic test bench for some of the electronics that are going to be used in the sonar, that are difficult to evaluate and to access once they are assembled.

An automatic test bench has two major advantages: first, the tests are done as efficient as they can be, without having to measure and check things by hand. Second, it avoids human errors by taking the operator out of the loop, relegating her or him to manage a user interface used to manage the tests and receive the results.

# **Objectives**

The aim of this project is to program the microprocessor of the test bench to allow testing of all interfaces of the RX32 electronics card. The test bench will be used at the supplier's side of the electronics card and in the factory at Ostend. The test bench will be able to send back voltage information, send signals and "loop through" the GPIO's (Vynckier, 2022, p. 5).

More precisely, the specific targets of this thesis due to the proximity of deadlines, complexity of the final product and the unavailability of some crucial pieces (like the electronics to test) are reduced to do previous research about the feasibility of the idea, lay the foundations for the development of the test bench and mainly to **test the concept** of the project.

This thesis is therefore meant to be the groundwork for the development of the functional automated test bench, that will be manufactured with the collaboration of a subcontractor in the near future.

### **Development timeline**

The project development (including this thesis) lasted a total of 17 weeks. The internship at ECA Robotics, where this project was created, covered a period of 14 of those weeks. The thesis and defence preparation took up the other 3 weeks, as it was established by VIVES University.

We can structure the internship period into three main parts:

- Weeks 1 to 5: All previous research, familiarization with the components, software and specifications, and initial documentation (scope and vision of the project, UML diagrams...) were made.

- Week 5: A restructuration of the project was necessary. The maximum priority was moved from making a completely functional test bench to test the concept for further development.

- Weeks 6 to 13: Development phase. All software for the test bench was created relaying on the previous research and agreed documentation.

- Week 9: The company organized a travel to the headquarters of ECA in Toulon.

There, we had a meeting with the subcontractor who is going to develop part of the project, as we will explain later. This meant a little rescope of the project.

- Weeks 13 and 14: Test phase and construction of the prototype. The final product was tested using this prototype. All documentation and manuals for further keeping up with the project by the next developers was finished and explained to the team.

The timeline in the Annexes (pg. 70 ) provides more details about the steps taken to finish this project.

### Structure of the document

In the next chapters we will discuss what an autonomous underwater vehicle, a sonar, an RX32, a test bench and a Nucleo-144 are. After that, we will explain the context of the project, go into the technical background, and give an overview of the time course of this project within our internship. At the end of the document, a clear conclusion is provided, along with the bibliography and annexes.

### Overview by chapter:

- Background: in this chapter crucial terms for understanding the project will be discussed.

The terminology that will be used, the detailed explanation of technologies that will be mentioned along this document and some historical contexts are the main points included in this part.

- **Context of the project**: this chapter aims to inform the reader about the scope of the project, locating it from the general context -naval mines countermeasures technology- to the specific target this thesis is focused on: the test bench for sonar electronics.

- Technical explanation: as the technical part of the project can be easily divided into a computer part (PC part) and an electronics-controlled part (Nucleo part), we will also divide this chapter in the exact same way. The chapter starts with a general overview and then goes through the software description following the data flow (PC→Communication→Nucleo). It includes the explanation of the development of the hardware too.

- **Timeline**: the purpose of this chapter is to locate the project in time. The reader will have a clear idea of how much time was dedicated to every part of the development and the sequence followed to build not only the software and hardware of the project, but all the documentation attached to it too.

# 2 Background

### **Autonomous Underwater Vehicle**

### **Terminology**

The Cambridge University Press Dictionary defines *drone* as "an aircraft that does not have a pilot but is controlled by someone on the ground, used especially for dropping bombs or for surveillance".

According to this definition an underwater robot could never be called a drone, as it is not an aerial vehicle or aircraft. However, the term *drone* is often widely used in all fields (civilian *and* military) for designating an autonomous driverless vehicle, regardless of the physical environment it was designed for. As a matter of fact, the leading companies in this project use the term *underwater drone* in their press releases. Taking this into consideration, the term *drone* will be used for any unmanned vehicle reference from now on.

Along with that, we must be careful when naming the subtypes of this kind of vehicles. A wrong use of the terminology can lead to confusion with acronyms and definitions.

To avoid that, the specific nomenclature listed below will be always followed in this document, and the differences and classification of these terms will be explained in detail further in this paper

- UUV: Unmanned Underwater Vehicle (U.S. Department of Defence, 2016).

- AUV: Autonomous Underwater Vehicle. Not to be mistaken with Unmanned Aerial Vehicle or UAV.

- ROV: Remotely Operated Vehicle.

### **Definitions and history**

To talk about autonomous underwater vehicles, we must first define what an unmanned underwater vehicle (UUV) is.

A UUV is a pilotless robot capable of operating underwater.

According to Siciliano & Khatib (2016, Chapter 25. Underwater Robots), nowadays most of commercially available UUVs are remotely operated through a cable coming from a mother vessel. These remotely operated vehicles, or ROVs, use this thread for power, control and sending information back from the sensors to the land or mothership operators.

On the other hand, the term autonomous underwater vehicle, or its more used acronym AUV, stands for submarine drones that can operate unthreaded without an on-board human operator.

In 1960, the US Navy founded an early ROV technology development. Since then, they have been used for a wide range of applications: from military operations to scientific missions, ocean mining and gas and oil industry. However, during the last two decades an increasing demand of a next

generation of ROVs appeared. Autonomous under water vehicles started to be developed in response to that demand (Siciliano & Khatib, 2016, Chapter 25. Underwater Robots).

### Sonar

### Definitions and terminology

Water is one of the most challenging environments for sensors. The light does not usually penetrate far in the water column, making optical sensing dependent on the turbidity level and therefore of limited use. Also, the electromagnetic wave propagation is extremely low range underwater, turning position sensing into a very difficult task too, as the GPS is not available (Siciliano & Khatib, 2016, Chapter 25.4 Underwater Actuators and Sensors).

Contrastingly, acoustic waves can travel long distances underwater without attenuating excessively. They can reach every depth in the oceans, from the deepest points in the Marianas Trench to the shallowest waters of the North Sea coast, just a few centimetres beneath the surface. This allows acoustic sensors to explore a range of more than 11 km deep, according to Blondel's Handbook of Sidescan Sonar (2009).

Acoustic sensors can collect three basic types of information: seafloor shape, seafloor reflectivity, and impedance changes in the sub-seafloor. All these types of acoustic data are provided by the sensors installed on platforms that, in combination, are referred to as sonar systems (Carton et al., 2017).

SONAR or Sound Navigation And Ranging hence is a technique for detecting and determining the distance and direction of objects located below the water surface by acoustic means (The Editors of Encyclopædia Britannica, 2019).

Despite being an acronym, *sonar* has become a word in its own right, and it is considered grammatically correct to write it lowercased.

Additional sonar-related definitions useful for understanding the following chapters are included below:

Hydrophone: underwater device that detects and records underwater sounds from all directions.

Most of them are based on a special property of ceramic materials that produces a small electrical current when the device is exposed to water pressure changes (NOAA, 2021).

Beam: line of energy, radiation or particles sent in a particular direction. Also used as *ping*: a short high-pitched resonant sound, as of a bullet striking metal or a sonar echo (HarperCollins Publishers, n.d).

Transceiver: both transmitter and receiver device.

Bathymetry: acoustic data that represents seafloor shape (Carton et al., 2017, p. 92).

### History

Some animal species have the capability of locating objects using sound waves. Well known examples of these animals are bats and dolphins. They do so by interpreting the echoes of the ultrasonic sounds they produce, using this skill to locate food and objects in their habitat. These kinds of animals have inspired humans to use similar technics.

According to Ainslie (2016, Chapter 1.1 WHAT IS SONAR?), the first electronic systems enabling detection and localisation were invented in the 20th century. The creation of these systems was motivated by the sinking of the RMS Titanic in 1912 and the First World War, incidents that drew attention to the lack of underwater object-localisation systems. The Second World War and the Cold War stimulated the further development of these systems into the high-performance sonars we have today.

### **Physical principles**

### Acoustic waves, propagation, and scattering

In his book, Blondel (2009) defines acoustic waves as the propagation of a pressure wave through an environment, characterized by its intensity, that is often measured in a logarithmic scale relative to the source (decibels or dB), its frequency and the length and type of the pulse.

The intensity is related to the changes in pressure and the frequency (f) is related to the wavelength( $\lambda$ ) by means of the velocity of the sound in the medium (c).

$$f = \frac{c}{\lambda}$$

In water, c ranges between 1,450m/s and 1,550m/s in seawater, and it is reliant on the salinity, pressure, and temperature of the water.

When acoustic waves are transmitted through a water column, they experience an attenuation, which depends on the travelled distance and the dissipation of the acoustic energy due to viscosity and chemical reactions in the medium. This decrease in intensity is much more important when acoustic waves encounter the seabed. This is used in the sonar imagery: more range means weaker acoustic returns.

### Signal emission and reception

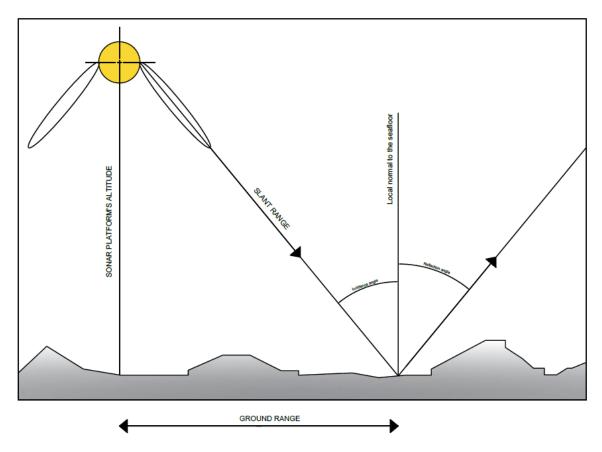

The beams transmitted by the sonar are projected both sides of the sonar. These beams are narrow along-track to acquire high resolution and wide across-track to improve the range of coverage.

Most of the energy will be reflected in the specular direction of the beam and only a small portion of it will be received back by the receivers of the sonar (backscatter). The information that can be extracted from this backscatter is the time offset between the transmission (ping) and the reception, that its directly proportional to the slant range. From the sonar height the ground range to the echo can be deduced, and phase shifts are used to measure the arrival angle of the beam.

Comparing the phase shift from two contiguous transducers some systems can also extract bathymetry. Also, the amplitude can give information about the nature of the imaged point (Blondel, 2009).

Figure 1: Adapted from Blondel, P. (2009a). Definitions of some parameters [Ilustration]. In The Handbook of Sidescan Sonar (p. 15).

### Classification

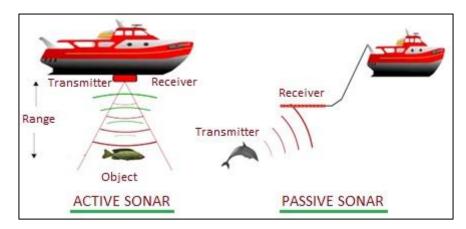

A first distinction is made between three different systems: active sonar, passive sonar, and acoustic communication systems.

Active sonar generates pulses that are reflected by the object. The reflected pulses are then picked up and analysed to determine the distance, bearing and relative movement of the target (Sonar | Definition, Acronym, Uses, & Facts, 1998).

Passive sonar analyses and identifies these features as well, interpreting both direction and distance of the sound it has listened through its receiver. This sound may come from vessels, marine life, submarines...

Figure 2 [Active SONAR vs Passive SONAR]. (n.d.). https://www.rfwireless-world.com/images/Active-SONAR-vs-Passive-SONAR.jpg

The third system, acoustic communication, requires a sound emitter and receiver on both sides of the link. This can be used to set up the communication of a submarine with a surface vessel.

Carton et al. (2017) make a second classification among the sonars that measure the seafloor reflectivity. This kind of measurement provides information about the texture, allowing to find objects on or right underneath the seabed as long as they have high acoustic contrast in relation to the surrounding environment.

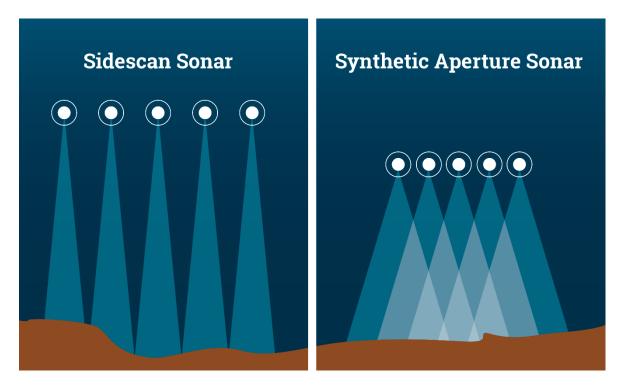

### Side-scan sonar (SSS)

These sonars project fan-shaped sound beams that reach an area that covers from beneath the projector to a point close to the horizon, called *nadir*. The projector transmits a ping, and the hydrophones will record back first the reflection from the nearest point, that will be the nadir in a flat bottom. The rest of the reflections will come from the closest to the furthest points and the strength of the signal will vary if an object with a different sound reflection, resulting into a strip of pixels. When the projector moves forward, it adds more strips creating a bidimensional image of the seafloor.

### Synthetic aperture sonar (SAS)

Synthetic aperture sonars are an emerging technology that aim to provide a high-resolution swath imagery of the seabed. These sonars follow the same principle as the SSS, emitting sound beams to both sides of the platform (wider pulses in SAS), but they combine successive acoustic pings along the known track to increase the apparent resolution along this track (azimuth resolution). The resulting image has a resolution of cm in an over hundreds of meters range.

SAS faces a lot of challenges, like unexpected changes of heigh and trajectory of the platform that must be compensated by a precise control of the platform where the sonar is mounted. Powerful algorithms and signal processing is necessary for a good performance of the sonar, that is never carried by the surface vessel, but in a towed platform behind a survey vehicle or an AUV to minimize the motion variations and better control the host vehicle attitude.

Figure 3: National Oceanic and Atmospheric Administration [NOAA]. (n.d.). Side-scan sonar vs synthetic aperture sonar pulses [Illustration]. National Oceanic and Atmospheric Administration (NOAA) Ocean Exploration. https://oceanexplorer.noaa.gov/technology/sonar/sas.html

The reason SAS in gaining popularity is mainly due to its versability. In the images acquired with these sonars the difference between soft and hard textures in the bottom of the seas can be observed. When these images are combined with depth measurement, an accurate bathymetry is obtained (interferometric synthetic aperture sonar). However, it has some disadvantages too. SAS is expensive to operate and requires very complicated processing of the data received. The trajectory the device follows must be pre-fixed to satisfy the assumptions for the calculations (National Oceanic and Atmospheric Administration [NOAA], n.d.-a).

### **RX32**

The RX32 is a small board, designed and made by a subcontractor. This board contains an FPGA, some LEDs and connectors, among other electronics. Several of these boards are used in the pulser and receiver of the sonar unit of the UUV, where they represent a critical part of the project. Once these boards are installed in the sonar unit, it is a time-consuming process to replace them. It is therefore essential to test and validate this part before installing it. In this project, the RX32 is plugged into the test bench using an interface card.

### **Test Bench**

### **Terminology**

A test bench or test bed is a term used by various disciplines to describe a platform or environment that is used for testing components, design, or models. A test bench is used to perform tests that produce transparent and reproducible results ("Testbed," 2022). There are two types of test benches, namely development test benches and end-of-line test benches. The test bench used in this thesis is an end-of-line test bench.

The overall purpose of this type of test bench is to check the function of newly developed test pieces. ECA Robotics Belgium chooses not only to check samples, for example a newly developed RX32, but to test every RX32. This can be seen as a general quality control ("Prüfstand," 2006).

### Nucleo-144

The Nucleo-144 is a development board manufactured by STMicroelectronics. This board is part of the STM32 Nucleo family and with its 144 pins is the largest of the family. For this project, the Nucleo-H7A3Z1-Q, based on an Arm® Cortex®-M7 core was chosen. It was selected because this board integrates a USB-Serial converter and a programmer/debugger for the microcontroller. For this project, it was suggested to plug the Nucleo-H7A3Z1-Q directly into the test bench, to avoid extra manipulation of the board and wires.

### About the manufacturer

STMicroelectronics is the result of a merger between the two semiconductor companies of the French and Italian governments. The merger took place in 1987 between the Italian company SGS Microelettronica and the French company Thomson Semiconducteurs (STMicroelectronics, 2022).

### **Features**

All STM32 Nucleo-144 boards share the following common features:

- STM32 microcontroller in LQFP144 package

- 3 user LEDs

- 2 user and reset push-buttons

- 32.768 kHz crystal oscillator

- Board connectors: SWDST Zio expansion connector including ARDUINO® Uno V3ST morpho expansion connector

- Flexible power-supply options: ST-LINK, USB V<sub>BUS</sub>, or external sources

- On-board ST-LINK debugger/programmer with USB re-enumeration capability: mass storage, Virtual COM port, and debug port

- Comprehensive free software libraries and examples available with the STM32Cube MCU Package

- Support of a wide choice of Integrated Development Environments (IDEs) including IAR Embedded Workbench®, MDK-ARM, and STM32CubeIDE

The following features are specific to this board:

- External or internal SMPS to generate V<sub>core</sub> logic supply

- Ethernet compliant with IEEE-802.3-2002

- USB OTG full speed or device only

- Board connectors: USB with Micro-AB or USB Type-C<sup>®</sup> Ethernet RJ45

- Arm<sup>®</sup> Mbed Enabled<sup>™</sup> compliant

(NUCLEO-H723ZG, n.d)

# 3 Context of the project

### What is a naval mine?

According to the Dictionary of Military and Associated terms of the U.S. Department of Defence (2016), a mine in a naval warfare context is an explosive device laid in the water with the intention of damaging or sinking ships or of deterring shipping from entering an area. The Official NATO Terminology Database adds to this definition that the term does not include devices attached to the bottoms of ships or to harbour installations by personnel operating underwater, neither devices that explode immediately on expiration of a predetermined time after laying (NATO, n.d.-a).

Nowadays, the two principal types of naval mines present in seas are moored and bottom mines:

A moored mine is a "contact or influence¹-operated mine of positive buoyancy held below the surface by a mooring attached to a sinker or anchor on the bottom" as is defined in the NATO Terminology Database. In the other hand, a bottom mine is a "mine with negative buoyancy which remains on the seabed" (NATO, n.d.-a).

Figure 4: ONI-37 & Naval History and Heritage Command. (n.d.). Floating Mine in the North Sea 123952 [Photograph]. Naval History and Heritage Command. https://www.history.navy.mil/

# The history of naval mine warfare

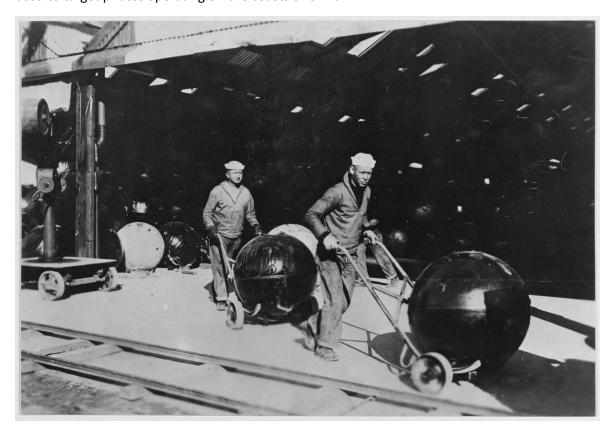

The Naval History and Heritage Command (2021) dates the first attempt of use of naval mine warfare back to the American Revolution, in 1777, when part of the British fleet was stationed at the Delaware River off Philadelphia. David Bushnell discovered a gunpowder capable of exploding underwater and was authorized by General George Washington to use it to destroy some of the enemy ships. The device failed but the attempt brought attention from all over the world to this underwater exploding device.

However, in the International Security Department Workshop about International Law Applicable to Naval Mines (Chatham House & The Royal Institute of International Affairs, 2014) the early

<sup>&</sup>lt;sup>1</sup> An influence mine is actuated by the effect of a target on some physical condition in the vicinity of the mine or on radiations emanating from the mine (NATO, n.d.-a).

precursors to sea mines are tracked back to the Ming dynasty, in the 16th century, where they were used to target pirates operating off the coasts of China.

Figure 5: Naval History and Heritage Command & Signal Corps 43589. (n.d.). Handling Mine cases. NH 123955 [Photograph]. Naval History and Heritage Command. https://www.history.navy.mil/

Naval mines were used in the upcoming wars, from the U.S Civil War to both the World Wars. These devices were used to sink vessels, destroy submarines and to restrict fleets movement across the sea (Naval History and Heritage Command, 2021), but it was not until the Russo-Japanese War (1904-1905) that they were used extensively (Chatham House & The Royal Institute of International Affairs, 2014). Because of this conflict, those neutral countries with important surface fleets were deeply concerned about the potential destructive power of naval mine warfare on their own ships. Concurrently, mines were blocking merchant shipping free navigation, causing disruptions that made the commercial trading interests to have them banned extensively (Chatham House & The Royal Institute of International Affairs, 2014).

In 1899, through the personal initiative of Tsar Nicholas II of Russia, a conference was convened in The Hague with the main purpose of limiting armaments. The posterior Hague Conference of 1907 was much more focused on naval affairs after both civil and military concerns. As it was said in the International Security Department Workshop, summarized by Chatham House & The Royal Institute of International Affairs in 2014, the commercial trading interests wanted an outright ban of naval mines. However, the Royal Navy saw naval interests in them and only wanted them restricted. Therefore, the British opinion favoured tight restrictions on mining activity instead of a total ban.

# Applicable regulations on naval mine warfare

According to the mine warfare publication of the U.S. Marine Corps and U.S. Navy (1996, pp. 1–7), "The Hague Convention (VIII) of 1907 probably had more of a legal impact on MIW than any other forum". The document also collects the specific provisions laid down by this convention:

- 1. Armed, unanchored mines must have a maximum life of 1 hour.

- 2. Armed, anchored mines must become unarmed if they break free from their moorings.

- 3. Mines must be designed to become harmless should they miss their target.

- 4. It is illegal to mine solely against commercial shipping.

- 5. Neutral nations are not to be interfered with, and the safe transit of neutral shipping must be ensured.

- 6. Mines must be removed by the planting force at the conclusion of hostilities.

Furthermore, the Convention states that the mine-laying states are required to notify neutral states as to the dangers that exist to innocent shipping unless the mines laid are controlled mines that are used only to target military objectives. But, since the obligation to notify must be made as soon as military exigencies permit, the failure to notify immediately does not automatically constitute a violation of international law (Haines, 2014, "IV. E. Article 4" section).

In addition, even though the specific international laws set forth during the Hague Convention remain in effect today, as it is also said in the in the above-mentioned document that "they have not always been adhered to by all nations, and world events have seen major deviations from these principles".

# Reality of current underwater mine warfare threats

These days, naval mines still remain a danger for civilian and military ships. The lack of knowledge of the exact location and number of these mines make the countermeasure missions difficult and newly placed mines that have drifted away by the sea currents can become a danger outside the countries in conflict.

Sadly, there are plenty of examples of this problem today. The newspaper CE Noticias Financieras reports that "The Bulgarian government has warned about the presence of explosive mines drifting in the Black Sea that were allegedly washed up from the Ukrainian city of Odessa endangering maritime traffic in the area". According to the Bulgarian Executive, they "were swept away by a storm and are floating in the Black Sea posing a threat to all vessels" (Content Engine LLC, 2022).

And this is not the only case across the Black Sea. The Ghana News Agency (GNA) also reports the detection of another naval mine off the coast of Kefken, in Istanbul, following the discovery of two other mines at the end of March (SyndiGate Media Inc, 2022).

That is why, even for countries that are not currently participants of an armed conflict, mine countermeasures (or MCM) have crucial importance among the naval operations conducted by military forces.

# **Nowadays Mine Countermeasures (MCM)**

MCM can be offensive (proactive) or defensive (enabling). This project's scope lays on the defensive mine countermeasures, that can be also classified into active and passive. Passive defensive MCM includes all measures that reduce the effectiveness of the mine without physically removing it. Active measures remove the mine, by destroying it or neutralizing it (U.S. Marine Corps & U.S. Navy, 1996).

The two main subsets of active MCM are mine hunting and mine sweeping. According to the naval warfare publication of the U.S. Marine Corps and U.S. Navy (1996), mine hunting actions individually locate the mines for countermeasures to be taken, while in mine sweeping, all the mines in the sweep path are addressed at the same time.

In that document is also stated that the mine hunting process is done by detecting the mines for them to be later classified, located, identified using video camera and sonar, and neutralized. The mine disposal is done by using an explosive charge to cause the detonation of the mine.

For many European countries MCM has been a high priority, mainly because of the mines left over from the Cold War and the World Wars. Specifically, the Netherlands and Belgium constitute one of the strongest NATO allies, and it has been stated by the U.S. Marine Corps and the U.S. Navy (even from 1996) that they are perhaps "the best MCM school in the world".

# **Future of MCM: Belgium Naval & Robotics**

In 2021, it was announced that the Ministry of Defence of the Netherlands contract from the Defence Material Organization (DMO), was awarded to the Naval Group and ECA Group consortium (Called Belgium Naval & Robotics). The project is meant for the supply of a drone system for mine hunting capable of replacing the Dutch Navy (Belgium Naval & Robotics, 2021).

In a 2018 press release from ECA Group, it is stated that the partnership created in 2018 "will bring together the skills of Naval, European leader in naval defence, responsible for designing, supplying, and maintaining military vessels carrying drones, with those of ECA Group, a robotics specialized Group with expertise in mine warfare developed over several decades, responsible for designing and providing resources that may be launched into minefields (drones, sonars, etc.)".

The collaboration, born 60 years ago, is extended to integrate  $UMIS^{TM}$  Toolbox into the Naval Group vessels for developing the next generation of MCM.

# The mine-hunter drone system for BE/NL<sup>2</sup> Navy

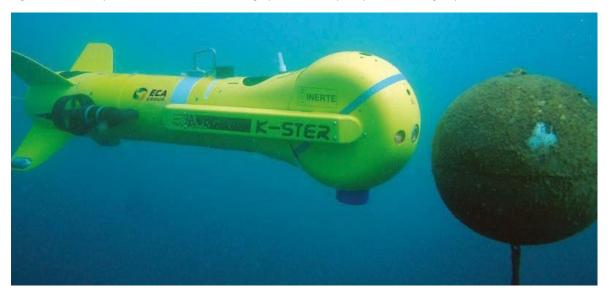

The project aims to preform safe MCM operations from a distant vessel using unmanned systems. The mission starts from a Mine Countermeasures warship, that deploys a USV (Figure 6) into the mine zone, keeping human operators out of danger. The USV can launch an AUV (Figure 7) that tracks the mine locations using a powerful Synthetic Aperture Sonar (Figure 8) or a self-powered towed sonar (For further information refer to page 21), that uses the same technology to detect in real time, classify and map seabed and moored mines. For further identification, a ROV provided with a high-quality camera (Figure 9) gets closer to the mines, and after confirmation, another AUV (Figure 10) completes the neutralisation by exploding the mine (Belgium Naval & Robotics, 2020). A UAV is also included, mostly for communication purposes.

Figure 6: ECA Group. (n.d.). INSPECTOR 125 [Photograph]. ECA Group. https://www.ecagroup.com/en/solutions

Figure 7: ECA Group. (n.d.). A18-M [Photograph]. ECA Group. https://www.ecagroup.com/en/solutions

-

<sup>&</sup>lt;sup>2</sup> Belgium and Netherlands

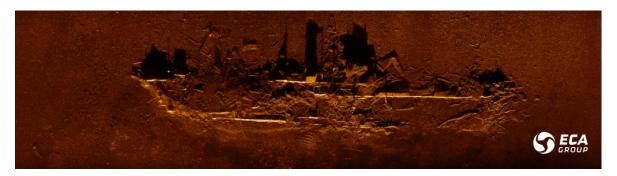

Figure 8: ECA Group. (n.d.). Image obtained with SAS [Photograph]. ECA Group. https://www.ecagroup.com/en/solutions

Figure 9: ECA Group. (n.d.). SEASCAN MK2 [Photograph]. ECA Group. https://www.ecagroup.com/en/solutions

Figure 10: ECA Group. (n.d.). K-STER [Photograph]. ECA Group. https://www.ecagroup.com/en/solutions

Figure 11: ECA Group. (n.d.). UMISAS Toolbox [Ilustration]. ECA Group. https://www.ecagroup.com/en/solutions

### **UMISTM** sonar: **UMISAS**

The SAS system mounted on the AUV in charge of the localization of the mines (the A18-M and the T18-M) is called UMISAS, and uses a technique protected by an ECA group patent.

The UMISAS sonars are interferometric synthetic aperture sonars (InSAS<sup>3</sup>) that aim to obtain a spatial resolution of 3cm x 3cm in order to better classify small and irregular objects, as it is said in the ECA group webpage describing the A18-M features.

There, it is also highlighted that the UMISAS sonar does not use the navigation sensors dedicated to the sonar present in the market, since they are less efficient, do not allow geo-referencing of the images formed and are, above all, less reliable. UMISAS uses the drone itself inertial unit to preform SAS processing.

-

<sup>&</sup>lt;sup>3</sup> For further explanation refer to page 14.

Figure 12: ECA Group. (2021, March 31). UMISAS 120 VHF sonar image of S.S. Ferrando collected off the coast of Hyères, France. [Photograph]. Belgium Naval & Robotics. https://www.belgium-naval-and-robotics.be/sucessful-sea-trials-ecagroup-umisas-sonar/

### The electronics of SAS and the approach of their testing

Each antenna of the SAS has sets of transmitters that emit the sound pulse and sets of receivers that listen back. Part of the electronics of these antennas is made up of RX32 cards.

For the first stage of this project, the predicted quantity of RX32 cards to be mounted on the SAS of the drones to be delivered to the BE/NL Navy amounts up to several hundreds of units. Each unit of RX32 card must perform under demanding environments without flaws, and furthermore, it must not fail once installed on the antenna.

The testing of electronic components before assembling them together is always a crucial part of the production of any device. In this scenario, the RX32 are mounted in places that are difficult to access for the operator. If a card is installed and the fault is only detected after testing the whole SAS, it must be dismantled in a high time-consuming process, not knowing if the error comes from that card or not.

Moreover, the number of units of these cards in each antenna makes the process of removing damaged units and replacing them an even more tedious and slow procedure, that could delay the production of the drones unnecessarily.

Due to these constraints, it is deeply important that all RX32 are flawlessly tested before their final integration into the system. Furthermore, because of the high number of units to be tested, it is also important that the tests are executed as fast and with as less interaction from the operator as possible to avoid human mistakes.

As a result of all of this, the solution reached was to build a test bench capable of automatically perform all necessary tests by just plugging the card onto it and interacting with the system through an intuitive computer interface where the operator can select the tests and see the results in a simple and fast way.

Hence, the scope of this thesis focuses on the automation of such test bench, and specifically on the software and hardware developed for that purpose and how it was designed to being able to incorporate the parts created by other teams, both inside and outside the company.

# 4 Technical explanation

### **General view**

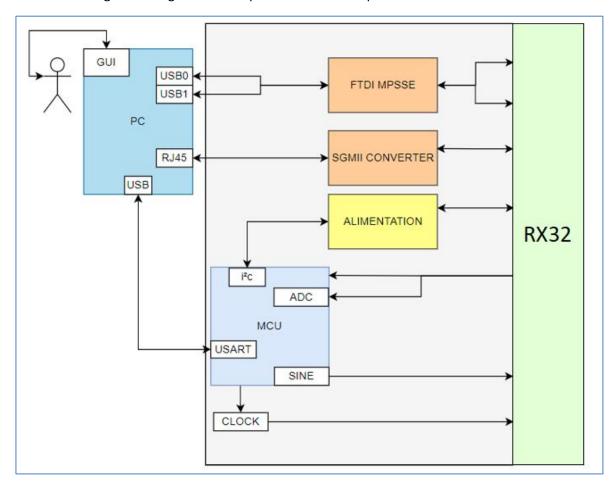

The following set-up is used for the development and automatization of the test bench.

The set-up consists of two major parts, namely a computer on which a GUI (general user interface) was programmed and a test bench consisting of a circuit board on which an RX32 is plugged. The RX32 is the component to be tested in this set-up. The communication between the computer and the test bench goes through three USB ports and one RJ45 port.

Figure 13: Software overview diagram

The operation of the set-up takes the following steps. A command is given to the test bench via the GUI. After the test bench received the command, the command is processed by the test bench. The result of the processing is sent back to the computer and can be read in the GUI. Based on the result, it can be checked whether the RX32 reacted as expected or not.

### **Project vision and scope**

As agreed with the company, the product will be used to automatically preform the test of the RX32 card. It will have a simple interface for the user to select the test and visualize the information. It will produce a report in PDF form with the test results.

- 1) The system must automatically preform the required tests for checking the correct performance of the UUT<sup>4</sup>.

- User interaction to select the test.

- Execute the test commands in correct order.

- Run the provided scripts.

- Send/receive digital and analog signals to/from UUT and peripherals.

- 2) The system must check if the UUT passed the test or not.

- Compare the obtained results with the expected ones.

- 3) The system must draw up a report containing the test results.

- Read the SN of the UUT.

- Elaborate a report file in PDF displaying test and UUT information.

- Print/export the report file.

- Show test results on screen.

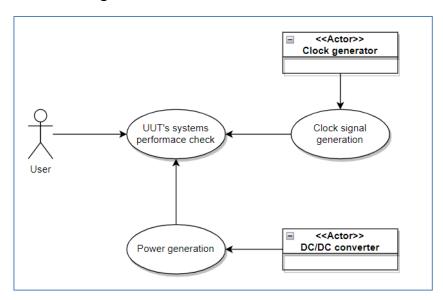

### Use cases

### Actor and target identification

| Extern event                    | Actor                  | Target                                                     |

|---------------------------------|------------------------|------------------------------------------------------------|

| Select the test to be preformed | User                   | Check the correct performance of the UUT system's elements |

| Generate power                  | DC/DC converter        | Generate the correct voltages for the UUT                  |

| Generate a clock signal         | Extern clock generator | Send a specific clock signal for some tests                |

Table 1: Actor and target identification

\_

<sup>&</sup>lt;sup>4</sup> Unit Under Test.

### Use cases diagram

Figure 14: Use cases diagram

# **UUT's systems performance check**

| Actor:              | User.                                                                                    |

|---------------------|------------------------------------------------------------------------------------------|

| Description:        | Check if UUT is working properly and ready to be used.                                   |

| Preconditions:      | The UUT is properly connected to all specified devices.                                  |

|                     | The MCU is connected and responding.                                                     |

| Postconditions:     | Test results report.                                                                     |

|                     | 1.0 The user connects the system and the UUT and starts the PC program.                  |

|                     | 2.0 The system sends an ECHO message to the MCU and waits for it to respond ok.          |

| Normal course:      | 3.0 Opens the interface and selects the test/tests to be performed on the unit.          |

|                     | 4.0 The system preforms the selected test/s.                                             |

|                     | 5.0 The user waits till the test is finished.                                            |

|                     | 6.0 The test ends, the report is produced, and results are showed in screen.             |

| Alternative course: | 3.1 Interaction between user and system. The user wants to send a command to the Nucleo. |

|                     | 2.0.E.1 The MCU is not responding (no/wrong ECHO message). [Stop system]                 |

| Exceptions:         | 3.0.E.1 The scripts couldn't be run or returned error. [Test No OK]                      |

|                     | 3.0.E.2 There is an error on any peripherals. [Stop system]                              |

| Includes:           | Power generation. Clock generation.                                                      |

| Priority:            | Maximum. System core. |

|----------------------|-----------------------|

| Notes and documents: | Test results report.  |

Table 2: Use case. UUT's systems performance check

### **Power generation**

| Actor:              | DC/DC converter                                                             |

|---------------------|-----------------------------------------------------------------------------|

| Description:        | Generate the different necessary power voltages to supply the UUT.          |

| Preconditions:      | A test has been selected.                                                   |

| Postconditions:     | Power supply is generated and delivered to the UUT.                         |

| Normal course:      | 1.0 The user selects a test.                                                |

|                     | 2.0 The system generates power when requested.                              |

|                     | 3.0 The system sends a feedback current.                                    |

|                     | 4.0 The system stops generating power when requested.                       |

| Alternative course: | -                                                                           |

| Exceptions:         | 3.0.E.1 The system can't send a feedback current. An error message is sent. |

|                     | 3.0.E.2 The system can't power some pin/s (short-circuit, no poweretc). An  |

|                     | error message is sent specifying witch one is in fault state.               |

| Includes:           | -                                                                           |

| Priority:           | Medium. System peripheral.                                                  |

| Notes and           | -                                                                           |

| documents:          |                                                                             |

Table 3: Use cae. Power generation

# **Clock signal generation**

| Actor:          | Extern clock generator                                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

| Description:    | Generate a clock signal of a certain frequency and send it to the UUT.                                                           |

| Preconditions:  | Test where is used is selected.                                                                                                  |

| Postconditions: | A clock signal is generated and delivered to the UUT.                                                                            |

| Normal course:  | <ul><li>1.0 The user selects one of the specified tests.</li><li>2.0 The system generates clock signal when requested.</li></ul> |

|                 | 2.0 The system generates clock signal when requested.                                                                            |

|                      | 3.0 The system stops generating the clock signal when requested. |

|----------------------|------------------------------------------------------------------|

| Alternative course:  | -                                                                |

| Exceptions:          | -                                                                |

| Includes:            | -                                                                |

| Priority:            | Medium. System peripheral.                                       |

| Notes and documents: | -                                                                |

Table 4: Use case. Clock signal generation

#### **UML** diagrams

See annexes (pg. 71).

#### **Complementary specifications**

- 1. Programming languages: C for MCU and for the PC application.

- 2. Platforms: Linux (Ubuntu 16.04).

- 3. Data storage: Database.

- 4. Report template must contain the date and name of the user performing the test, the SN of the UUT and the test results for each test (OK, no OK and N/A).

#### Sharing of the design process between the parties

As mentioned before in this document, as the project was not meant to be finished before our internship finished, the company came to an agreement with a subcontractor to develop part of the low-level software for the Nucleo board and the main part of the hardware of the testbench.

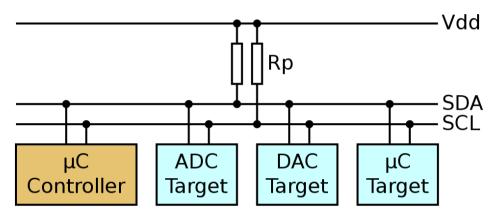

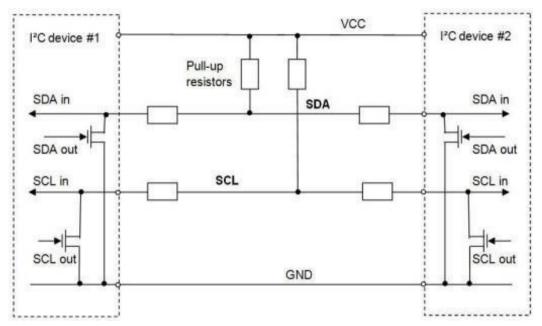

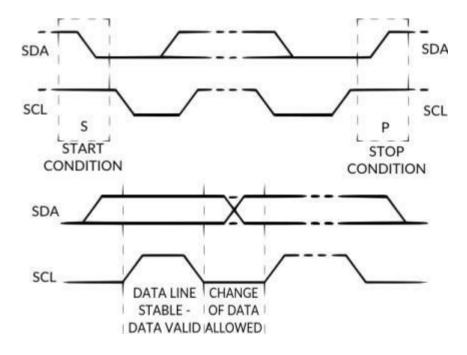

All PC parts were designed by us, and all drivers for the Nucleo too, except for the Input Capture, Watchdog and I2C drivers, that will be provided by this subcontractor.

## Communication

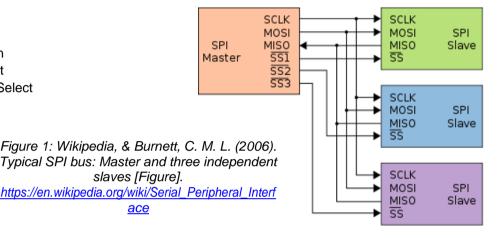

The communication between the computer on which the GUI is programmed and the test bench on which the RX32 is plugged in runs through 4 ports. There are 3 USB ports and 1 RJ45 port.

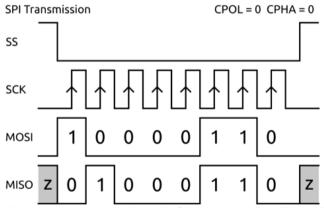

Within this project the focus of communication lays on the connection between the computer and the NUCLEO. The computer and NUCLEO are connected via USB port.

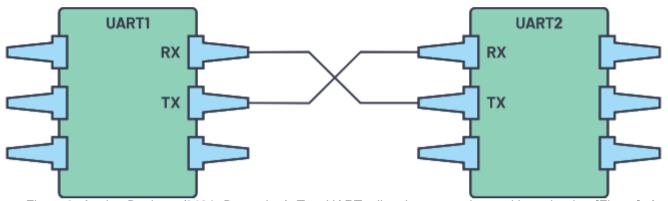

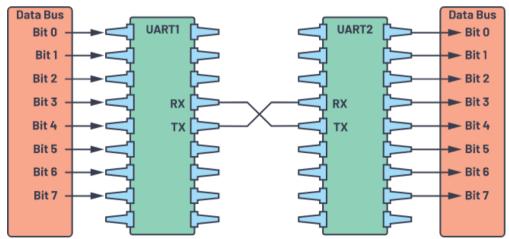

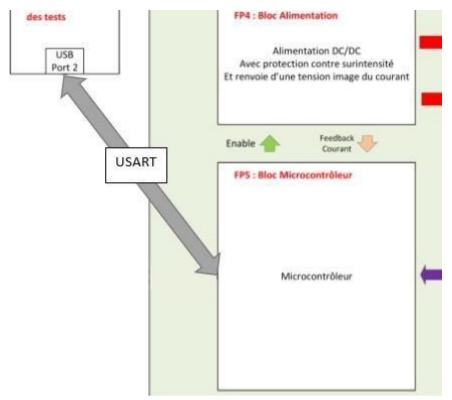

Initially, the communication between the computer and NUCLEO was done via USART (universal synchronous/ asynchronous receiver/ transmitter). The disadvantage of USART is that the ring buffer is not present by default but had to be programmed. An attempt was made to program a ring buffer, but this did not succeed. During some tests, it was noticed that the communication between the computer and NUCLEO via USART was not optimal cause the computer did not receive

all the data, and to be able to properly develop and automate the test bench, it is of great importance that all data is received properly. For this reason, a switch was made to an USB OTG (USB on-the-go). The advantage of this device is that a ring buffer is built in. After adding the USB OTG, the communication between the computer and the Nucleo was much better. The computer received all the results without any problems.

The election of the communication technology was carefully studied and reported to the company in a document called "PC-MCU communication comparison" that is included in the Annexes (pg.76).

#### **Protocol**

To standardise the communication between the PC and the Nucleo, it was decided to develop a protocol of our own. The protocol contains all the necessary commands that will be needed to carry out the tests. These commands are made up of different symbols, follow strict rules and must be formatted correctly.

The rules to which the command must adhere are as follows:

- Command is case sensitive.

- All commands have a response.

All consists of 3 capital letters. Each command consists of a header, command, parameters, and an end character with a delimiter between each block. At the very end, a new line character is required before the command can be properly interpreted. If these blocks are correctly assembled, a command will look like this:

- Header: Contains one single character that indicates the direction of the message: Nucleo to PC or PC to Nucleo.

- CMD: All commands must be 3 letters.

- PARAM: All the parameters needed for the command separated by commas: <p1,p2,p3,...>

- INFO: '!' or '?'. Execute an action or ask for information.

The following symbols are defined in the protocol:

- C → Header of command for messages coming from the PC.

- N → Header of command for messages coming from the Nucleo.

- : → Separator.

- → Separator of parameters.

- ? → Query for response.

- ! → Query for action.

- In → End of message (managed by the USART OTG in this application).

# PC part

## **Coding language**

As mentioned earlier, the commands to the test bench were given through a GUI programmed on the computer. The programming of the GUI was done by the developers themselves, using the coding language C. In addition, the GTK library was used to render the GUI. the choice of coding language depended on the operating system that would be used. The ECA company and developers preferred Linux as the operating system. This was because it was expected that the scripts coming from the external company might have been written in several other coding languages. The developers expected that there would be fewer problems in executing these scripts on Linux than on Windows. Within Linux, the developers had experience with the C coding language and Javascript. Since ECA has less experience with Javascript than with C, C was chosen as the coding language for this project

#### Code

The code is composed of several parts. In what follows, the parts are discussed step by step. The discussion of the parts follows the process by which the different parts are covered. The whole thing will be illustrated using an example so that the operation of the code becomes clear.

The main function is the most important function of all. This function is the start and end of the programme. A control system always calls on the main when the programmer executes his code.

The second part of the code to be discussed is the GUI. The GUI is the platform through which developers can send commands to the test bench. The developers can issue commands as follows. First, the developer must select the NUCLEO. This way, the computer knows which NUCLEO to pass the command to. Next, the developer must enter the serial number of the RX32. The purpose of entering the serial number is to find out which tests were performed on which RX32. Third, the developer needs to select the test folder. Here it is important that the developer places the correct test in the test folder before running the test. To run the test, the developer needs to press play. While running the test, the GUI displays the received data. If necessary, the user can enter commands manually. He can do this by entering a command in the right pane and after which he should click 'send'. After the user has done this, the command will be executed. Even then, the GUI will display the received data.

The third part of the code is the USB. Via USB, a communication channel is established between the GUI and chardev (Nucleo). Through this channel, the GUI can send commands to the Nucleo and the GUI receives responses from the Nucleo

The fourth part of the code is the test sequencer. The test sequencer plays a very central role within the entire code. The test sequencer comes into action after the user has entered all the information in the GUI (including which tests they want to run) and the user runs the tests.

Once the user has done this, the test sequencer goes through 3 steps.

- In step 1, the test sequencer looks at which tests to run.

- In step 2, the test sequencer reads and runs the tests one at a time. The sequencer checks what the name and number of the test is. In addition, it examines what command should be given to the Nucleo and indicates what response it expects from the Nucleo. Once the data is collected, the test sequencer executes the test. In doing so, it sends the commands of the test in question to the Nucleo. Then the test sequencer compares the responses received from the Nucleo with the responses the test sequencer expected in advance. If the responses received are equal to the expected responses, the test sequencer moves on to the next test and the steps described above are repeated on the next test. If the responses received do not equal the expected responses, the test sequencer repeats the commands. If the test sequencer has sent out the commands three times, but the responses received still differ from the expected responses, the test sequencer stops sending out the commands of this particular test and moves on to the next test. Once all tests have been performed, the test sequencer moves on to step 3.

- In step 3, the results obtained are reported. These results are stored by the test sequencer in a struct.

The fifth part of the code is pdf. After the test has been run, the results of these tests can be accessed in a pdf document. This pdf document is automatically generated after the tests are run. The title of the pdf document is always the serial number of the RX32. In this way the results of the tests can always be linked to the correct RX32.

The document provides the following information: serial number of the RX32, which tests were run, whether the tests were successful or not, date, time.

As previously indicated, an error message 'Nok' will be given if a test generates responses other than the expected responses after three attempts. If a test takes less than three attempts to generate the same responses as the expected response, the test will be rated as 'okay'.

The results of the tests performed can not only be found in the pdf documents. In addition to the pdf documents, a database is also created. This sixth part of the code collects the results of the tests performed per RX32. The difference with the pdf documents is in the display of the results. The results are displayed per test performed in a very clear and visual way in the pdf documents. In the database, the results are also displayed in an orderly fashion, but in a slightly less visually friendly way. Nevertheless, the database has a great advantage in certain situations. Suppose a test is run several times at the same RX32, the database allows the results of the different runs to be displayed in a table. The pdf documents cannot give this info. In fact, a new pdf document will be created for each run. The results of the different tests, will not be able to be displayed at a glance.

'General' is the last subdivision of the code. In this section, a number of functions are grouped together. A first function is 'timestamp'. This function displays the date and time. A second function is 'regex'. The function 'regex' is used to check whether the entered data is qualitative. More specifically, it checks whether the serial number of the RX32 can be correct. The last function 'listport' lists all serial devices. This is important to be able to find NUCLEO.

## **Serial connection**

The Nucleo behaves like a serial device that is connected, via USB On-The-Go, to the computer.

In Linux everything is regarded as a file or document so that the same functions can be used as with a normal text document. However, within Linux, the Nucleo is recognised as a character device. Because of this, extra configuration is needed to open the file that the Nucleo represents. The configuration uses the POSIX terminal control or thermios.h header file to set up serial communication. After the configuration is complete, the PC can access the information transmitted by the Nucleo without any problems. When processing the information, the following process is always repeated:

- 1. opening the filepointer

- 2. configuring the filepointer

- 3. reading the filepointer

- 4. closing the filepointer

In a normal text file, the file pointer remains open until all necessary actions are processed. In the current setup, the decision was made to close the file pointer after each action and then open it again. This is because otherwise a large part of the CPU capacity is taken up.

## **Test sequencer**

The test sequencer is a state machine that reads the test file and sends the commands to the Nucleo.

Figure 15: Flowchart of Test sequencer

When the correct test folder is chosen in the GUI and play is pressed, you will arrive at status 1 within the test sequencer.

## Status 1

In status 1 the number of tests is compared to the number of tests that were run. If no tests have been run yet, the test sequencer reads the first test and increases the status by 1. After 500 milliseconds (see also GTK mainloop and single threating) the sequencer switches to status 2.

## Status 2

In state 2 the test sequencer sends the command and the state is increased again by 1. After that status 3 is reached.

#### Status 3

In state 3 a comparison is made between the response received and the response expected. In addition, it is also checked whether not all commands were executed. If this is the case, the test sequencer goes to state 2 and state 2 is repeated.

If not, the test sequencer checks whether all commands have been completed. If all commands are completed, it goes to status 1 and repeats status 1.

If not, status 3 is run through again. Status 3 can be run through a maximum of three times. If status 3 is not successfully completed after 3 times, the test sequencer switches to status 100.

## Status 100

In status 100 an error is reported. After that the sequencer switches to status 1 where the next test is read.

#### Status 6

When all tests have been completed, the test sequencer changes to state 6. In status 6 the data are saved in the database and the pdf is generated.

After the report, the test sequencer is reset and is ready to run through the next test sequence.

# **GTK main loop and single Threading**

It would be ideal if one could receive data from the Nucleo at any time, send data, iterate the test sequencer and perform other events like clicking buttons at the same time. Using the GTK API, one can do this without introducing too much effort or vulnerabilities into the code.

GTK provides Glib. Glib is a library that offers, among other things, main loop abstraction. From this library two functions are used.

- idle add

- timeout\_add

```

while (!done)

{

if (serialport > 0)

{

if (flag)

{

g_idle_add((GSourceFunc)reading, &serialport);

g_idle_add((GSourceFunc)readUpdate, DATA_BACKptr);

// om de 500ms volgende functie oproepen:

g_timeout_add(500, (GSourceFunc)testsequencer, NULL);

flag = 0;

}

}

```

Figure 16: GLib functions in main loop GUI

#### idle add

This function makes the given function an event which will be called when there is no event with a higher priority ("GLib.Idle\_add," 2022). This function is used twice in the code. Once for the "continuous" reading or receiving of data sent by the Nucleo and a second time for updating the buffer which is used to visualise the received data in the GUI.

#### timeout add

With timeout\_add one can set an interval when the specified function should be called ("GLib.Timeout\_add," 2022). In the code this function is used to iterate the test sequencer every 500 ms.

#### **Test**

The tests used in the test sequencer are constructed according to the following rules:

Line one and two are reserved for the name and number of the test.