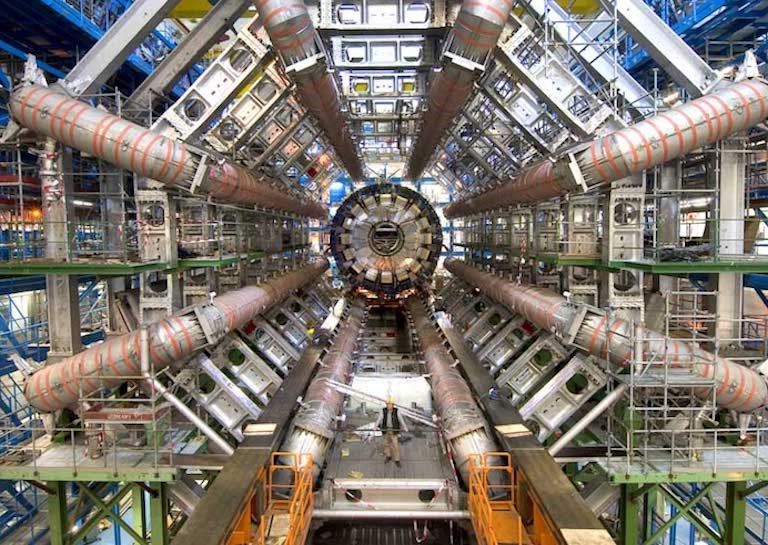

Meetrobots voor uitzonderlijke stralingsomgevingen

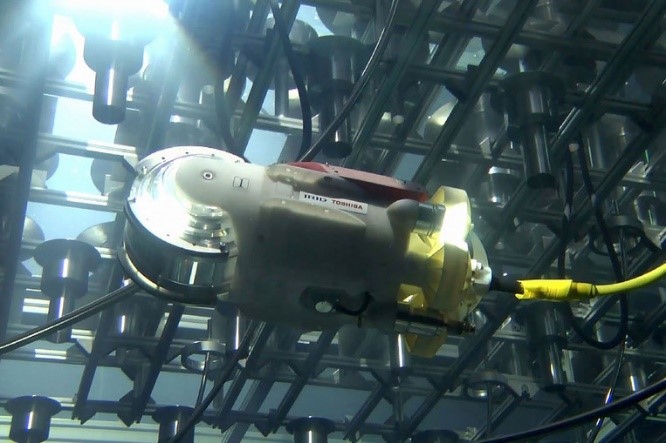

Traditionele microchips zijn niet betrouwbaar en hebben een korte levensduur wanneer ze worden blootgesteld aan straling. Omdat onbruikbare of foute data ten alle moet worden vermeden is er een oplossing nodig voor dit probleem. Deze oplossing heeft tevens als resultaat dat alle handelingen die voordien door mensen gebeurden, kunnen overgenomen worden door robots.

De omgeving binnen de deeltjesversneller in CERN, de reactor van een kerncentrale en zelfs de ruimte zijn onderhevig aan uitzonderlijke straling. Dat maakt het uitvoeren van handelingen zoals metingen of inspecties extreem gevaarlijk voor de gezondheid van de mens. Daarom wordt vaak gebruik gemaakt van robots voor het uitvoeren van deze handelingen. Robots ondervinden echter ook problemen in deze uitzonderlijke stralingsomgevingen. De blootstelling aan straling vermindert de levensduur en betrouwbaarheid van de elektronica. Omdat nauwkeurige metingen van cruciaal belang zijn, gebeurt er steeds meer onderzoek naar het bestand maken van deze gevoelige elektronica tegen straling.

Het verwerken van de opgemeten signalen gebeurt met een digitale processor. Daarom is er nood aan een conversie van het analoge signaal, afkomstig van de sensor, naar zijn digitale voorstelling. Een analoog-digitaal convertor of ADC verwezenlijkt deze conversie. Vaak zal de ADC geïntegreerd worden in de microprocessor, rechtstreeks aan de ingang waar het analoge signaal de processor binnen komt.

De studie, zoals beschreven in de scriptie: ‘Ontwerp van een SAR ADC voor nucleaire toepassingen’, onderzoekt de mogelijkheid voor het ontwerp van een analoog-digitaal convertor bestand te maken tegen straling. Het schematisch ontwerp van de ADC zal worden besproken van begin tot einde. Het volledige circuit is getest op verschillende parameters. Na het classificeren van de ADC zijn verschillende state-of-the-art technieken onderzocht voor het bestand maken van het circuit tegen ioniserende straling.

Het resultaat van deze studie kan worden toegepast in verschillende componenten van robots zodat metingen nauwkeurig en betrouwbaar zullen plaatsvinden. De gebruikte technieken zouden de betrouwbaarheid en levensduur moeten doen toenemen met een factor duizend.

Bibliografie

[1] T. Anderson. Optimum Control Logic for Successive Approximation Analog-to-Digital Convertors.

In JPL TECHNICAL REPORT, pages 168–176, 1972.

[2] N. Atkinson, R. Blaine, J. Kauppila, S. Armstrong, T. Loveless, N. Hooten, W. Holman, L. Massengill,

and J. Warner. RHBD Technique for Single-Event Charge Cancellation in Folded-

Cascode Amplifiers. In IEEE TRANSACTIONS ON NUCLEAR SCIENCE, volume 60, pages

2756–2761, 2013.

[3] M. Bhargava, M. McCartney, M. Hoefler, and K. Mai. Low-Overhead, Digital Offset Compensated,

RAM Sense Amplifiers. In IEEE 2009 Custom Intergrated Circuits Conference (CICC),

pages 705–708, 2009.

[4] J. Blair. Histogram Measurement of ADC Nonlinearities Using Sine Waves. In IEEE TRANSACTIONS

OF INSTRUMENTATION AND MEASUREMENT, volume 53, pages 373–383,

1994.

[5] T. Carusone, D. Johns, and K. Martin. Analog Integrated Circuit Design. John Wiley & sons,

2013.

[6] L. Chen, A. Sanyal, J. Ma, X. Tang, and N. Sun. Comparator Common-Mode Variation Effects

Analysis and its Application in SAR ADCs. In 2016 IEEE International Symposium on Circuits

and Systems (ISCAS), pages 2014–2017, 2016.

[7] Y. Chen, X. Zhu, M. Kibune, Y. Tomita, T. Hamada, M. Yoshioka, K. Ishikawa, T. Takayama,

J. Ogawa, S. Tsukamato, and T. Kuroda. Split Capacitor DAC Mismatch Calibration in Successive

Approximation ADC. In IEEE 2009 Custom Intergrated Circuits Conference (CICC),

pages 279–282, 2009.

[8] J. Doernberg, H. Lee, and D. Hodges. Full-Speed Testing of A/D Convertors. In IEEE JOURNAL

OF SOLID-STATE CIRCUITS, volume 19, pages 820–827, 1984.

[9] M. Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, A. Klumperink, and B. Nauta. A 10-bit

Charge-Redistribution ADC Consuming 1.9 μW at 1 MS/s. In IEEE JOURNAL OF SOLIDSTATE

CIRCUITS, volume 45, 2010.

[10] B. Ginsburg and A. Chandrakasan. An Energy-Efficient Charge Recycling Approach for a SAR

Converter With Capacitive DAC. In Circuits and Systems, 2005. ISCAS 2005, pages 184–187,

2005.

[11] W. Guo and S. Mirabbasi. A Low-Power 10-bit 50-MS/s SAR ADC Using a Parasitic-

Compensated Split-Capacitor DAC. In 2012 IEEE International Symposium on Circuits and

Systems, pages 1275–1278, 2012.

12] S. Haenzsche, S. Henker, and R. Sch¨ uffny. Modelling of Capacitor Mismatch and Non-

Linearity Effects in Charge Redistribution SAR ADCs. In MIXDES 2010, 17th Intarnational

Conference ”Mixed Design of Integrated Circuits and Systems”, pages 300–305, 2010.

[13] R. Hedayati. A Study of Successive Approximation Registers and Implementation of an Ultra-

Low Power 10-bit SAR ADC in 65nm CMOS Technology. Master thesis, Link¨oping University,

2011.

[14] C. Huang, H. Ting, and S. Chang. Analysis of Nonideal Behaviors Based on INL/DNL Plots

for SAR ADCs. In IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT,

volume 65, pages 1804 – 1817, 2016.

[15] S. Kang, Y. Leblebici, and C. Kim. CMOS Digital Integrated Circuits: Analysis & Design.

McGraw-Hill Education, fourth edition, 2015.

[16] C. Liu, S. Chang, G. Huang, and Y. Lin. A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor

Switching Procedure. In IEEE JOURNAL OF SOLID-STATE CIRCUITS, volume 45, pages

731–740, 2010.

[17] K. Lundberg. Analog-to-Digital Convertor Testing. http://www.mit.edu/people/klund/

A2Dtesting.pdf, 2002.

[18] S. M., R. Lotfi, K. Mafinezhad, and W. Serdijn. Analysis of Power Consumption and Linearity

in Capacitive Digital-to-Analog Converters Used in Successive Approximation ADCs. In IEEE

TRANSACTIONS ON CIRCUITS AND SYSTEMS, volume 58, pages 1736–1748, 2011.

[19] K. Murotatsu and K. Fujiyoshi. Adjacent Common Centroid Placement for Analog IC Layout

Design. In Asia Pacific Conference on Circuits and Systems (APCCAS), pages 619–622,

2014.

[20] P. Nuzzo, F. De Bernardinis, P. Terreni, and G. Van der Plas. Noise Analysis of Regenerative

Comparators for Reconfigurable ADC Architectures. In IEEE TRANSACTIONS ON CIRCUITS

AND SYSTEMS, volume 55, 2008.

[21] P. Otfinowski, P. Grybo´s, and R. Kleczek. A 10-bit 3MS/s Low-power Charge Redistribution

ADC in 180nm CMOS for Neural Application. In MIXDES 2011, 18th International Conference

”Mixed Design of Integrated Circuits and Systems”, pages 197–200, 2011.

[22] B. Razavi. Design of Analog CMOS Integrated Circuits. McGraw-Hill Education, 2001.

[23] X. She and K. McElvain. Time Multiplexed Triple Modular Redundancy for Single Event Upset

Mitigation. In IEEE TRANSACTIONS ON NUCLEAR SCIENCE, volume 56, pages 2443–

2448, 2009.

[24] S. Thys. ”Ontwerp van een SRAM gebaseerde sensor voor ioniserende straling in 0.18μm

CMOS-technologie. Master thesis, KU Leuven, 2016.

[25] D. Toro, F. Seguin, M. Arzel, and M. J´ez´equel. Study of a cosmic ray impact on combinatorial

logic circuits of an 8bit SAR ADC in 65nm CMOS technology. In IEEE 56th International

Midwest Symposium on Circuits and Systems (MWSCAS), pages 241–244, 2013.

[26] S. Vaseghi. Advanced Digital Signal Processing and Noise Reduction: Fourth edition. John

Wiley & sons, 2008.

[27] I. Villanueva and A. Lopez-Martin. An Ultra Low Energy 8-bit Charge Redistribution ADC for

Wireless Sensors. In Seventh International Conference of Sensing Technology, pages 199–

202, 2013.

[28] W. Xu and E. Friedman. Clock Feedthrough in CMOS Analog Transmission Gate Switches. In

15th Annual IEEE International ASIC/SOC Conference, pages 181–185, 2002.